# System Description Wireless Power Transfer

**Volume I: Low Power**

**Part 1: Interface Definition**

Version 1.0.1

October 2010

# System Description Wireless Power Transfer

**Volume I: Low Power**

**Part 1: Interface Definition**

Version 1.0.1

October 2010

#### **COPYRIGHT**

This System Description Wireless Power Transfer is published by the Wireless Power Consortium, and has been prepared by the Wireless Power Consortium in close co-operation with ConvenientPower Ltd., Fulton Innovation LLC, National Semiconductor Corporation, Nokia Corporation, Olympus Imaging Corporation, Research In Motion, Limited, Royal Philips Electronics, Sanyo Electric Co. Ltd., Shenzhen Sang Fei Consumer Communications Co. Ltd., and Texas Instruments Inc.. All rights are reserved. Reproduction in whole or in part is prohibited without express and prior written permission of the Wireless Power Consortium.

#### **DISCLAIMER**

The information contained herein is believed to be accurate as of the date of publication. However, neither the Wireless Power Consortium, nor ConvenientPower Ltd., nor Fulton Innovation LLC, nor National Semiconductor Corporation, nor Nokia Corporation, nor Olympus Imaging Corporation, nor Research In Motion Limited, nor Royal Philips Electronics, nor Sanyo Electric Co. Ltd., nor Shenzhen Sang Fei Consumer Communications Co. Ltd., nor Texas Instruments Inc. will be liable for any damages, including indirect or consequential, from use of this System Description Wireless Power Transfer or reliance on the accuracy of this document.

#### **NOTICE**

For any further explanation of the contents of this document, or in case of any perceived inconsistency or ambiguity of interpretation, or for any information regarding the associated patent license program, please contact: <a href="mailto:info@wirelesspowerconsortium.com">info@wirelesspowerconsortium.com</a>.

## **Table of Contents**

| 1 (        | Gene           | eral                                                                |    |

|------------|----------------|---------------------------------------------------------------------|----|

| 1.1        | Sco            | ppe                                                                 | 1  |

| 1.2        | Ma             | in features                                                         | 1  |

| 1.3        | Coi            | nformance and references                                            | 1  |

| 1.4        |                | finitions                                                           |    |

| 1.5        |                | onyms                                                               |    |

| 1.6        |                | nbols                                                               |    |

| 1.7        | -              | nventions                                                           |    |

|            | 1.7.1          | Cross references                                                    |    |

| 1          | 1.7.2          | Informative text                                                    |    |

|            | 1.7.3          | Terms in capitals                                                   |    |

|            | 1.7.4<br>1.7.5 | Notation of numbers                                                 |    |

|            | 1.7.5<br>1.7.6 | Units of physical quantitiesBit ordering in a byte                  |    |

|            | 1.7.7          | Byte numbering                                                      |    |

|            | 1.7.8          | Multiple-bit Fields                                                 |    |

| 1.8        | . On           | erators                                                             | 5  |

|            | 1.8.1          | Exclusive-OR                                                        |    |

|            | 1.8.2          | Concatenation                                                       |    |

| 2 9        | Svst           | em Overview (Informative)                                           | 7  |

|            | -              | c Power Transmitter Designs                                         |    |

| 3.1        |                | roduction                                                           |    |

| 3.2        | Pov            | wer Transmitter designs that are based on a single Primary Coil     | 11 |

| _          | 3.2.1          | Power Transmitter design A1                                         | 11 |

| 3          | 3.2.2          | Power Transmitter design A2                                         |    |

| 3.3        | Pov            | wer Transmitter designs that are based on an array of Primary Coils | 20 |

|            | 3.3.1          | Power Transmitter design B1                                         | 20 |

| 3          | 3.3.2          | Power Transmitter design B2                                         | 26 |

| <b>4</b> ] | Pow            | er Receiver Design Requirements                                     | 29 |

| 4.1        | Int            | roduction                                                           | 29 |

| 4.2        | Pov            | wer Receiver design requirements                                    | 30 |

|            | 4.2.1          | Mechanical requirements                                             |    |

| 4          | 4.2.2          | Electrical requirements                                             |    |

| 5 9        | Svst           | em Control                                                          | 35 |

| 5.1        | -              | roduction                                                           |    |

| 5.2        |                |                                                                     |    |

| _          | 5.2.1          | wer Transmitter perspectivePing phase                               |    |

|            | 5.2.2          | Identification & configuration phase                                |    |

|            | 5.2.3          | Power transfer phase                                                |    |

| 5.3        | Pos            | wer Receiver perspective                                            | 46 |

|            | 5.3.1          | Selection phase                                                     |    |

|            | 5.3.2          | Ping phase                                                          |    |

|            |                | 01                                                                  |    |

|    | 5.3.3          | Identification & configuration phase                    |     |

|----|----------------|---------------------------------------------------------|-----|

|    | 5.3.4          | Power transfer phase                                    | 48  |

| 6  | Com            | munications Interface                                   | 51  |

| 6. | 1 Int          | roduction                                               | 51  |

| 6. | 2 Phy          | rsical and data link layers                             |     |

|    | 6.2.1          | Modulation scheme                                       |     |

|    | 6.2.2          | Bit encoding scheme                                     |     |

|    | 6.2.3<br>6.2.4 | Byte encoding schemePacket structure                    |     |

|    |                |                                                         |     |

| 6. | -              | gical layer<br>Signal Strength Packet (0x01)            |     |

|    | 6.3.1<br>6.3.2 | End Power Transfer Packet (0x02)                        |     |

|    | 6.3.3          | Control Error Packet (0x03)                             |     |

|    | 6.3.4          | Rectified Power Packet (0x04)                           |     |

|    | 6.3.5          | Charge Status Packet (0x05)                             |     |

|    | 6.3.6          | Power Control Hold-off Packet (0x06)                    |     |

|    | 6.3.7          | Configuration Packet (0x51)                             |     |

|    | 6.3.8          | Identification Packet (0x71)                            |     |

|    | 6.3.9          | Extended Identification Packet (0x81)                   |     |

| An | nex A          | A Example Power Receiver Designs (Informative)          | 61  |

| A  | .1 Pov         | ver Receiver example 1                                  | 61  |

|    | A.1.1          | Mechanical details                                      | 61  |

|    | A.1.2          | Electrical details                                      | 62  |

| A  | .2 Pov         | ver Receiver example 2                                  | 64  |

|    | A.2.1          | Mechanical details                                      |     |

|    | A.2.2          | Electrical details                                      | 65  |

| An | nex E          | 3 Object Detection (Informative)                        | 67  |

| В  | .1 Res         | sonance shift                                           | 67  |

| В  | .2 Cap         | pacitance change                                        | 68  |

| An | nex (          | Power Receiver Localization (Informative)               | 69  |

| C. |                | ded Positioning                                         |     |

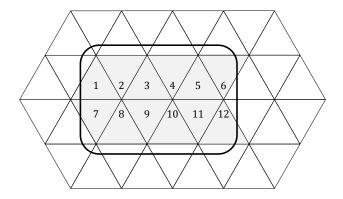

| C. | 2 Pri          | mary Coil array based Free Positioning                  | 69  |

| Ċ. | C.2.1          | A single Power Receiver covering multiple Primary Cells | 69  |

|    | C.2.2          | Two Power Receivers covering two adjacent Primary Cells |     |

|    | C.2.3          | Two Power Receivers covering a single Primary Cell      |     |

| C. | 3 Mo           | ving Primary Coil based Free Positioning                | 71  |

| An | nex I          | Metal Object Detection (Informative)                    | 73  |

| An | nex E          | •                                                       |     |

|    |                |                                                         | , O |

## **List of Figures**

| Figure 1-1: Bit positions in a byte                                                           |         |

|-----------------------------------------------------------------------------------------------|---------|

| Figure 1-2: Example of multiple-bit field                                                     | 5       |

| Figure 2-1: Basic system overview                                                             |         |

| Figure 3-1: Functional block diagram of Power Transmitter design A1                           | 11      |

| Figure 3-2: Primary Coil of Power Transmitter design A1                                       | 12      |

| Figure 3-3: Primary Coil assembly of Power Transmitter design A1                              | 13      |

| Figure 3-4: Electrical diagram (outline) of Power Transmitter design A1                       |         |

| Figure 3-5: Functional block diagram of Power Transmitter design A2A2                         | 16      |

| Figure 3-6: Primary Coil of Power Transmitter design A2                                       | 17      |

| Figure 3-7: Primary Coil assembly of Power Transmitter design A2                              | 18      |

| Figure 3-8: Electrical diagram (outline) of Power Transmitter design A2                       | 19      |

| Figure 3-9: Functional block diagram of Power Transmitter design B1B1                         |         |

| Figure 3-10: Primary Coil array of Power Transmitter design B1                                | 21      |

| Figure 3-11: Primary Coil array assembly of Power Transmitter design B1B1                     | 22      |

| Figure 3-12: Electrical diagram (outline) of Power Transmitter design B1B1                    |         |

| Figure 3-13: Multiple type B1 Power Transmitters sharing a multiplexer and Primary Coil array |         |

| Figure 3-14: Primary Coil array of Power Transmitter design B2                                |         |

| Figure 4-1: Example functional block diagram of a Power Receiver                              |         |

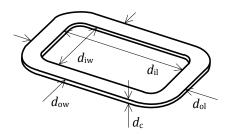

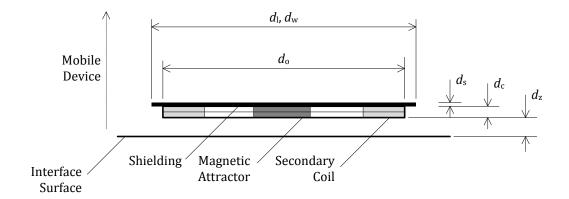

| Figure 4-2: Secondary Coil assembly                                                           |         |

| Figure 4-3: Dual resonant circuit of a Power Receiver                                         |         |

| Figure 4-4: Characterization of resonant frequencies                                          |         |

| Figure 5-1: Power transfer phases                                                             |         |

| Figure 5-2: Power transfer control loop                                                       |         |

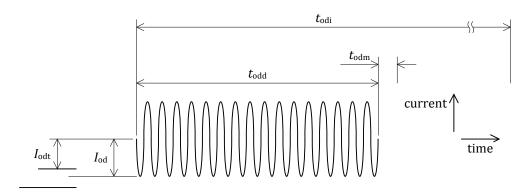

| Figure 5-3: Power Transmitter timing in the <i>ping</i> phase                                 |         |

| Figure 5-4: Power Transmitter timing in the identification & configuration phasephase         |         |

| Figure 5-5: Power Transmitter timing in the power transfer phase                              |         |

| Figure 5-6: PID control algorithm                                                             |         |

| Figure 5-7: Power Receiver timing in the selection phase                                      |         |

| Figure 5-8: Power Receiver timing in the <i>ping</i> phase                                    | 47      |

| Figure 5-9: Power Receiver timing in the identification & configuration phasephase            |         |

| Figure 5-10: Power Receiver timing in the power transfer phase                                |         |

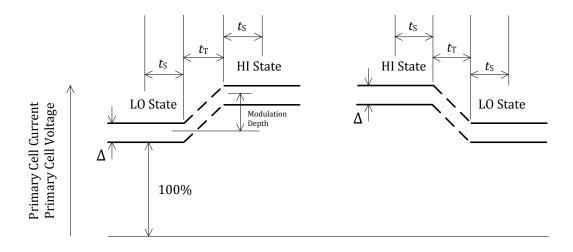

| Figure 6-1: Amplitude modulation of the Power Signal                                          |         |

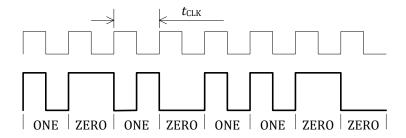

| Figure 6-2: Example of the differential bi-phase encoding                                     |         |

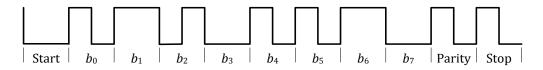

| Figure 6-3: Example of the asynchronous serial format                                         |         |

| Figure 6-4: Packet format                                                                     |         |

| Figure A-1: Secondary Coil of Power Receiver example 1                                        |         |

| Figure A-2: Secondary Coil and Shielding assembly of Power Receiver example 1                 |         |

| Figure A-3: Electrical details of Power Receiver example 1                                    |         |

| Figure A-4: Li-ion battery charging profile                                                   |         |

| Figure A-5: Secondary Coil of Power Receiver example 2                                        |         |

| Figure A-6: Secondary Coil and Shielding assembly of Power Receiver example 2                 |         |

| Figure A-7: Electrical details of Power Receiver example 2                                    |         |

| Figure B-1: Analog ping based on a resonance shift                                            |         |

| Figure C-1: Single Power Receiver covering multiple Primary Cells                             |         |

| Figure C-2: Two Power Receivers covering two adjacent Primary Cells                           |         |

| Figure C-3: Two Power Receivers covering a single Primary Cell                                |         |

| Figure C. 4. Detection Coil                                                                   | 7<br>72 |

## **List of Tables**

| Table 3-1: Primary Coll parameters of Power Transmitter design A1               | 12 |

|---------------------------------------------------------------------------------|----|

| Table 3-2: PID parameters for Operating Frequency control                       | 14 |

| Table 3-3: Operating Frequency dependent scaling factor                         | 14 |

| Table 3-4: PID parameters for duty cycle control                                | 15 |

| Table 3-5: Primary Coil parameters of Power Transmitter design A2               | 17 |

| Table 3-6: PID parameters for voltage control                                   |    |

| Table 3-7: Primary Coil array parameters of Power Transmitter design B1         |    |

| Table 3-8: PID parameters for voltage control                                   | 24 |

| Table 3-9: Primary Coil array parameters of Power Transmitter design B2         | 26 |

| Table 5-1: Power Transmitter timing in the ping phase                           |    |

| Table 5-2: Power Transmitter timing in the identification & configuration phase | 41 |

| Table 5-3: Power control hold-off time                                          | 41 |

| Table 5-4: Power Transmitter timing in the power transfer phase                 | 44 |

| Table 5-5: Power Receiver timing in any phase                                   | 46 |

| Table 5-6: Power Receiver timing in the selection phase                         | 47 |

| Table 5-7: Power Receiver timing in the identification & configuration phase    | 48 |

| Table 5-8: Power Receiver timing in the power transfer phase                    | 49 |

| Table 6-1: Amplitude modulation of the Power Signal                             | 52 |

| Table 6-2: Message size                                                         | 53 |

| Table 6-3: Packet types                                                         | 54 |

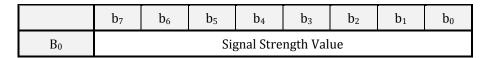

| Table 6-4: Signal Strength                                                      | 55 |

| Table 6-5: End Power Transfer                                                   |    |

| Table 6-6: End Power Transfer values                                            |    |

| Table 6-7: Control Error                                                        | 57 |

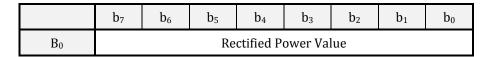

| Table 6-8: Rectified Power                                                      |    |

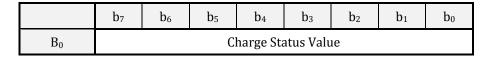

| Table 6-9: Charge Status                                                        |    |

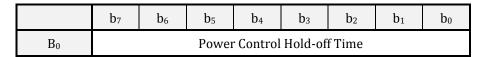

| Table 6-10: Power control hold-off                                              |    |

| Table 6-11: Configuration                                                       | 58 |

| Table 6-12: Identification                                                      |    |

| Table 6-13: Extended Identification                                             |    |

| Table A-1: Secondary Coil parameters of Power Receiver example 1                |    |

| Table A-2: Parameters of the Secondary Coil of Power Receiver example 2         |    |

| Table B-1: Analog ping based on a resonance shift                               | 67 |

| Table E-1: Changes from Version 1.0 to Version 1.01                             | 75 |

Version 1.0.1 General

#### 1 General

#### 1.1 Scope

Volume I of the System Description Wireless Power Transfer consists of the following documents:

- Part 1, Interface Definition.

- Part 2, Performance Requirements.

- Part 3, Compliance Testing.

This document defines the interface between a Power Transmitter and a Power Receiver.

#### 1.2 Main features

- A method of contactless power transfer from a Base Station to a Mobile Device, which is based on near field magnetic induction between coils.

- Transfer of around 5 W of power, using an appropriate Secondary Coil (having a typical outer dimension of around 40 mm).

- Operation at frequencies in the 110...205 kHz range.

- Support for two methods of placing the Mobile Device on the surface of the Base Station:

- Guided Positioning helps a user to properly place the Mobile Device on the surface of a Base Station that provides power through a single or a few fixed locations of that surface.

- Free Positioning enables arbitrary placement of the Mobile Device on the surface of a Base Station that can provide power through any location of that surface.

- A simple communications protocol enabling the Mobile Device to take full control of the power transfer.

- Considerable design flexibility for integration of the system into a Mobile Device.

- Very low stand-by power achievable (implementation dependent).

#### 1.3 Conformance and references

All specifications in this document are mandatory, unless specifically indicated as recommended or optional or informative. To avoid any doubt, the word "shall" indicates a mandatory behavior of the specified component, i.e. it is a violation of this System Description Wireless Power Transfer if the specified component does not exhibit the behavior as defined. In addition, the word "should" indicates a recommended behavior of the specified component, i.e. it is not a violation of this System Description Wireless Power Transfer if the specified component has valid reasons to deviate from the defined behavior. And finally, the word "may" indicates an optional behavior of the specified component, i.e. it is up to the specified component whether to exhibit the defined behavior (without deviating there from) or not.

In addition to the specifications provided in this document, product implementations shall also conform to the specifications provided in the System Descriptions listed below. Moreover, the relevant parts of the International Standards listed below shall apply as well. If multiple revisions exist of any System Description or International Standard listed below, the applicable revision is the one that was most recently published at the release date of this document.

| [Part 2] | System Description Wireless Power Transfer, Volume I, Part 2, Performance Requirements. |

|----------|-----------------------------------------------------------------------------------------|

| [Part 3] | System Description Wireless Power Transfer, Volume I, Part 3, Compliance Testing. $ \\$ |

| [PRMC]   | Power Receiver Manufacturer Codes, Wireless Power Consortium.                           |

General Version 1.0.1

[SI] The International System of Units (SI), Bureau International des Poids et

Mesures.

1.4 Definitions

Active Area The part of the Interface Surface of a Base Station respectively Mobile Device

through which a sufficiently high magnetic flux penetrates when the Base

Station is providing power to the Mobile Device.

Base Station A device that is able to provide near field inductive power as specified in this

System Description Wireless Power Transfer. A Base Station carries a logo to visually indicate to a user that the Base Station complies with this System

Description Wireless Power Transfer.

Communications and Control Unit

The functional part of a Power Transmitter respectively Power Receiver that controls the power transfer. (Informative) *Implementation-wise, the Communications and Control Unit may be distributed over multiple subsystems of*

the Base Station respectively Mobile Device.

Control Point The combination of voltage and current provided at the output of the Power

Receiver, and other parameters that are specific to a particular Power Receiver

implementation.

Detection Unit The functional part of a Power Transmitter that detects the presence of a Power

Receiver on the Interface Surface.

Digital Ping The application of a Power Signal in order to detect and identify a Power

Receiver.

Free Positioning A method of positioning a Mobile Device on the Interface Surface of a Base

Station that does not require the user to align the Active Area of the Mobile

Device to the Active Area of the Base Station.

Guided Positioning A method of positioning a Mobile Device on the Interface Surface of a Base

Station that provides the user with feedback to properly align the Active Area of

the Mobile Device to the Active Area of the Base Station.

Interface Surface A flat part of the surface of a Base Station respectively Mobile Device that is

closest to the Primary Coil(s) respectively Secondary Coil.

Mobile Device A device that is able to consume near field inductive power as specified in this

System Description Wireless Power Transfer. A Mobile Device carries a logo to visually indicate to a user that the Mobile Device complies with this System

Description Wireless Power Transfer.

Operating Frequency The oscillation frequency of the Power Signal.

Operating Point The combination of the frequency, duty cycle and amplitude of the voltage that

is applied to the Primary Cell.

Packet A data structure that the Power Receiver uses to communicate a message to the

Power Transmitter. A Packet consists of a preamble, a header byte, a message, and a checksum. A Packet is named after the kind of message that it contains.

Power Conversion Unit

The functional part of a Power Transmitter that converts electrical energy to a

Power Signal.

Power Pick-up Unit The functional part of a Power Receiver that converts a Power Signal to

electrical energy.

Power Receiver The subsystem of a Mobile Device that acquires near field inductive power and

controls its availability at its output, as defined in this System Description Wireless Power Transfer. For this purpose, the Power Receiver communicates

its power requirements to the Power Transmitter.

Version 1.0.1 General

Power Signal The oscillating magnetic flux that is enclosed by a Primary Cell and possibly a

Secondary Coil.

Power Transfer Contract A set of boundary conditions on the parameters that characterize the power

transfer from a Power Transmitter to a Power Receiver. Violation of any of

these boundary conditions causes the power transfer to abort.

Power Transmitter The subsystem of a Base Station that generates near field inductive power and

controls its transfer to a Power Receiver, as defined in this System Description

Wireless Power Transfer.

Primary Cell A single Primary Coil or a combination of Primary Coils that are used to provide

a sufficiently high magnetic flux through the Active Area.

Primary Coil A component of a Power Transmitter that converts electric current to magnetic

flux.

Secondary Coil The component of a Power Receiver that converts magnetic flux to

electromotive force.

Shielding A component in the Power Transmitter respectively Power Receiver that

restricts magnetic fields to the appropriate parts of the Base Station

respectively Mobile Device.

#### 1.5 Acronyms

AC Alternating Current

AWG American Wire Gauge

DC Direct Current

lsb least significant bit

msb most significant bit

N.A. Not Applicable

PID Proportional Integral Differential

RMS Root Mean Square

UART Universal Asynchronous Receiver Transmitter

#### 1.6 Symbols

Capacitance parallel to the Secondary Coil [nF]

$C_{

m m}$  Capacitance in the impedance matching network [nF]  $C_{

m P}$  Capacitance in series with the Primary Coil [nF]  $C_{

m S}$  Capacitance in series with the Secondary Coil [nF]  $d_{

m S}$  Distance between a coil and its Shielding [mm]

$d_z$  Distance between a coil and the Interface Surface [mm]

$f_{

m CLK}$  Communications bit rate [kHz]  $f_{

m d}$  Resonant detection frequency [kHz]

$f_{\rm op}$  Operating Frequency [kHz]

$f_{\rm S}$  Secondary resonance frequency [kHz]

$I_{

m m}$  Primary Coil current modulation depth [mA]

*I*<sub>o</sub> Power Receiver output current [mA]

*I*<sub>P</sub> Primary Coil current [mA]

$L_{\rm m}$  Inductance in the impedance matching network [ $\mu$ H]

## **System Description**Wireless Power Transfer

Version 1.0.1

| $L_{ m P}$        | Primary Coil self inductance [μH]                                                 |

|-------------------|-----------------------------------------------------------------------------------|

| $L_{ m S}$        | Secondary Coil self inductance (Mobile Device away from Base Station) [μΗ]        |

| $L_{\mathrm{S}}'$ | Secondary Coil self inductance (Mobile Device on top of Base Station) [ $\mu H$ ] |

| $P_{ m PR}$       | Total amount of power received through the Interface Surface [W]                  |

| $P_{ m PT}$       | Total amount of power transmitted through the Interface Surface [W]               |

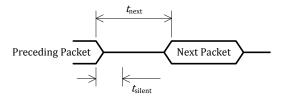

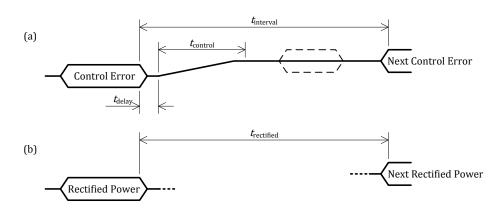

| $t_{ m delay}$    | Power Control Hold-off Time [ms]                                                  |

| $t_{ m CLK}$      | Communications clock period [μs]                                                  |

| $t_{ m T}$        | Maximum transition time of the communications [μs]                                |

| $V_{ m r}$        | Rectified voltage [V]                                                             |

| $V_{0}$           | Power Receiver output voltage [V]                                                 |

#### 1.7 Conventions

General

This Section 1.7 defines the notations and conventions used in this System Description Wireless Power Transfer.

#### 1.7.1 Cross references

Unless indicated otherwise, cross references to Sections in either this document or documents listed in Section 1.3, refer to the referenced Section as well as the sub Sections contained therein.

#### 1.7.2 Informative text

With the exception of Sections that are marked as informative, all informative text is set in italics.

#### 1.7.3 Terms in capitals

All terms that start with a capital are defined in Section 1.4. As an exception to this rule, Packet names and fields are defined in Section 6.3.

#### 1.7.4 Notation of numbers

Real numbers are represented using the digits 0 to 9, a decimal point, and optionally an exponential part. In addition, a positive and/or negative tolerance may follow a real number. Real numbers that do not include an explicit tolerance, have a tolerance of half the least significant digit that is specified. (Informative) For example, a specified value of  $1.23^{+0.01}_{-0.02}$  comprises the range from 1.21 through 1.24; a specified value of  $1.23^{+0.01}_{-0.02}$  comprises the range from 1.23 through 1.24; a specified value of  $1.23^{+0.01}_{-0.02}$  comprises the range from 1.21 through 1.23; a specified value of 1.23 comprises the range from 1.25 through 1.234999...; and a specified value of  $1.23^{\pm 10\%}_{-0.02}$  comprises the range from 1.107 through 1.353.

Integer numbers in decimal notation are represented using the digits 0 to 9.

Integer numbers in hexadecimal notation are represented using the hexadecimal digits 0 to 9 and A to F, and are preceded by "0x" (unless explicitly indicated otherwise).

Single bit values are represented using the words ZERO and ONE.

Integer numbers in binary notation and bit patterns are represented using sequences of the digits 0 and 1that are enclosed in single quotes ("). In a sequence of n bits, the most significant bit (msb) is bit  $b_{n-1}$  and the least significant bit (lsb) is bit  $b_0$ ; the most significant bit is shown on the left-hand side.

#### 1.7.5 Units of physical quantities

Physical quantities are expressed in units of the International System of Units [SI].

#### 1.7.6 Bit ordering in a byte

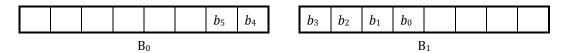

The graphical representation of a byte is such that the msb is on the left, and the lsb is on the right. Figure 1-1 defines the bit positions in a byte.

Version 1.0.1 General

Figure 1-1: Bit positions in a byte

#### 1.7.7 Byte numbering

The bytes in a sequence of n bytes are referred to as  $B_0$ ,  $B_1$ , ...,  $B_{n-1}$ . Byte  $B_0$  corresponds to the first byte in the sequence; byte  $B_{n-1}$  corresponds to the last byte in the sequence. The graphical representation of a byte sequence is such that  $B_0$  is at the upper left-hand side, and byte  $B_{n-1}$  is at the lower right-hand side.

#### 1.7.8 Multiple-bit Fields

Unless indicated otherwise, a multiple bit field in a data structure represents an unsigned integer value. In a multiple-bit field that spans multiple bytes, the msb of the multiple-bit field is located in the byte with the lowest address, and the lsb of the multiple-bit field is located in the byte with the highest address. (Informative) *Figure 1-2 provides an example of a 6-bit field that spans two bytes.*

Figure 1-2: Example of multiple-bit field

#### 1.8 Operators

This Section 1.8 defines the operators used in this System Description Wireless Power Transfer, which are less commonly used. The commonly used operators have their usual meaning.

#### 1.8.1 Exclusive-OR

The symbol '⊕' represents the exclusive-OR operation.

#### 1.8.2 Concatenation

The symbol '||' represents concatenation of two bit strings. In the resulting concatenated bit string, the msb of the right-hand side operand directly follows the lsb of the left-hand side operand.

## **System Description**Wireless Power Transfer

### 2 System Overview (Informative)

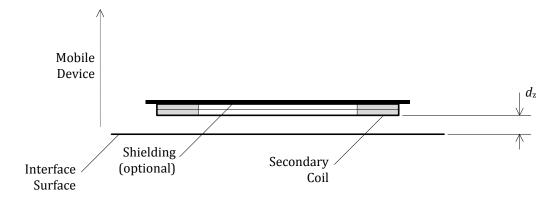

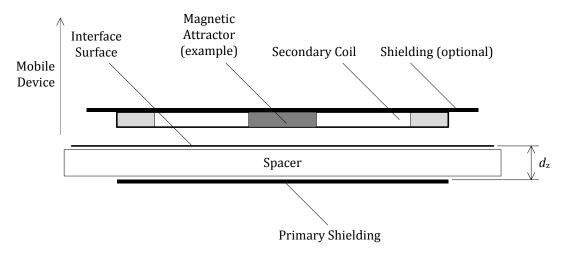

Operation of devices that comply with this System Description Wireless Power Transfer relies on magnetic induction between planar coils. Two kinds of devices are distinguished, namely devices that provide wireless power—referred to as Base Stations—and devices that consume wireless power—referred to as Mobile Devices. Power transfer always takes place from a Base Station to a Mobile Device. For this purpose, a Base Station contains a subsystem—referred to as a Power Transmitter—that comprises a Primary Coil, and a Mobile Device contains a subsystem—referred to as a Power Receiver—comprises a Secondary Coil. In fact, the Primary Coil and Secondary Coil form the two halves of a coreless resonant transformer. Appropriate Shielding at the bottom face of the Primary Coil and the top face of the Secondary Coil, as well as the close spacing of the two coils, ensures that power transfer occurs with an acceptable efficiency. In addition, this Shielding minimizes the exposure of users to the magnetic field.

Typically, a Base Station has a flat surface—referred to as the Interface Surface—on top of which a user can place one or more Mobile Devices. This ensures that the vertical spacing between Primary Coil and Secondary Coil is sufficiently small. In addition, there are two concepts for horizontal alignment of the Primary Coil and Secondary Coil. In the first concept—referred to as Guided Positioning—the user must actively align the Secondary Coil to the Primary Coil, by placing the Mobile Device on the appropriate location of the Interface Surface. For this purpose, the Mobile Device provides an alignment aid that is appropriate to its size, shape and function. The second concept—referred to as Free Positioning—does not require the active participation in alignment of the Primary Coil and Secondary Coil. One implementation of Free Positioning makes use of an array of Primary Coils to generate a magnetic field at the location of the Secondary Coil only. Another implementation of Free Positioning uses mechanical means to move a single Primary Coil underneath the Secondary Coil.

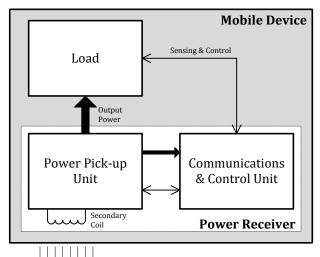

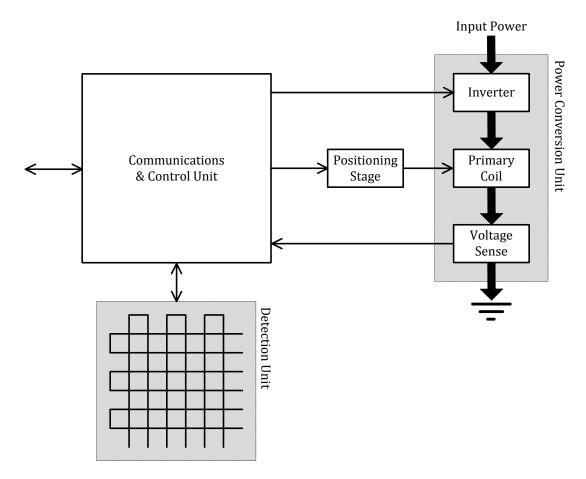

Figure 2-1 illustrates the basic system configuration. As shown, a Power Transmitter comprises two main functional units, namely a Power Conversion Unit and a Communications and Control Unit. The diagram explicitly shows the Primary Coil (array) as the magnetic field generating element of the Power Conversion Unit. The Control and Communications Unit regulates the transferred power to the level that the Power Receiver requests. Also shown in the diagram is that a Base Station may contain multiple Transmitters in order to serve multiple Mobile Devices simultaneously (a Power Transmitter can serve a single Power Receiver at a time only). Finally, the system unit shown in the diagram comprises all other functionality of the Base Station, such as input power provisioning, control of multiple Power Transmitters, and user interfacing.

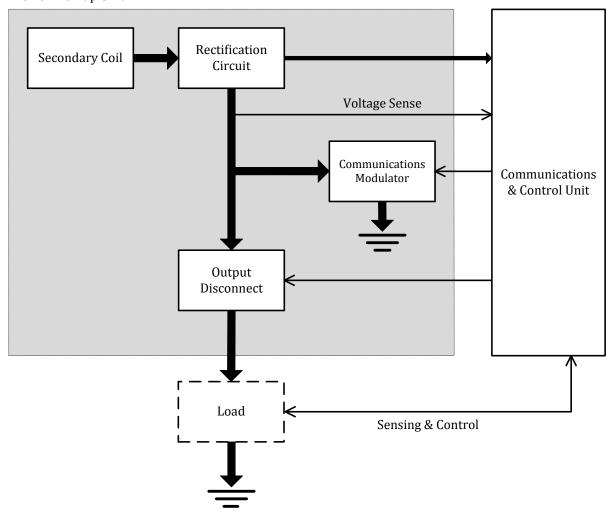

A Power Receiver comprises a Power Pick-up Unit and a Communications and Control Unit. Similar to the Power Conversion Unit of the Transmitter, Figure 2-1 explicitly shows the Secondary Coil as the magnetic field capturing element of the Power Pick-up Unit. A Power Pick-up Unit typically contains a single Secondary Coil only. Moreover, a Mobile Device typically contains a single Power Receiver. The Communications and Control Unit regulates the transferred power to the level that is appropriate for the subsystems connected to the output of the Power Receiver. These subsystems represent the main functionality of the Mobile Device. An important example subsystem is a battery that requires charging.

The remainder of this document is structured as follows. Section 3 defines the basic Power Transmitter designs, which come in two basic varieties. The first type of design—type A—is based on a single Primary Coil (either fixed position or moveable). The second type of design—type B—is based on an array of Primary Coils. Note that this version 1.0.1 of the System Description Wireless Power Transfer, Volume I, Part 1, offers only limited design freedom with respect to actual Power Transmitter implementations. The reason is that Mobile Devices exhibit a much greater variety of design requirements with respect to the Power Receiver than a Base Station does to Power Transmitters—for example, a smart phone has design requirements that differ substantially from those of a wireless headset. Constraining the Power Transmitter therefore enables interoperability with the largest number of mobile devices.

\_

<sup>&</sup>lt;sup>1</sup>Note that the Primary Coil may be a "virtual coil," in the sense that an appropriate array of planar coils can generate a magnetic field that is similar to the field that a single coil generates.

8

Figure 2-1: Basic system overview

Section 4 defines the Power Receiver design requirements. In view of the wide variety of Mobile Devices, this set of requirements has been kept to a minimum. In addition to the design requirements, Section 4 is complemented with two example designs in Annex A.

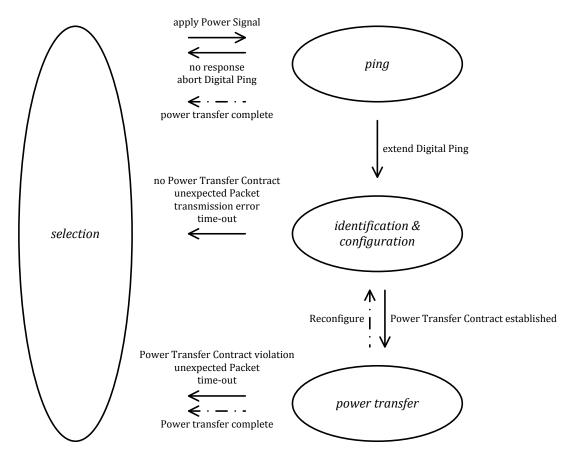

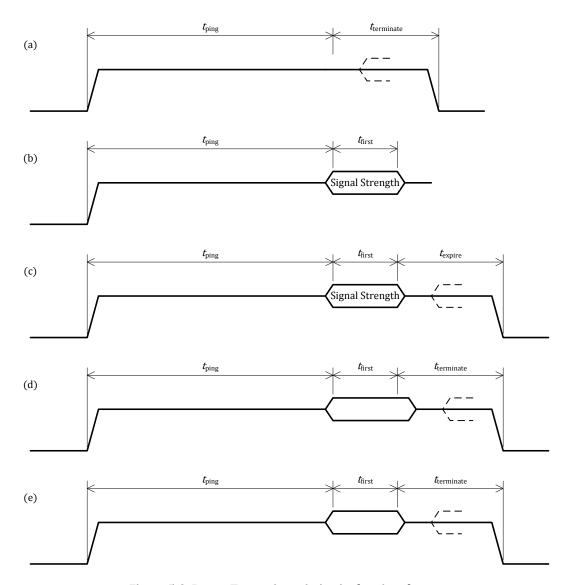

Section 5 defines the system control aspects of the power transfer. The interaction between a Power Transmitter and a Power Receiver comprises four phases, namely *selection*, *ping*, *identification* & *configuration*, and *power transfer*. In the *selection* phase, the Power Transmitter attempts to discover and locate objects that are placed on the Interface Surface. In addition, the Power Transmitter attempts to discriminate between Power Receivers and foreign objects and to select a Power Receiver (or object) for power transfer. For this purpose, the Power Transmitter may select an object at random and proceed to the *ping* phase (and subsequently to the *identification* & *configuration* phase) to collect necessary information. Note that if the Power Transmitter does not initiate power transfer to a selected Power Receiver, it should enter a low power stand-by mode of operation.<sup>2</sup> In the *ping* phase, the Power Transmitter attempts to discover if an object contains a Power Receiver. In the *identification* & *configuration* phase, the Power Transmitter prepares for power transfer to the Power Receiver. For this purpose, the Power Transmitter retrieves relevant information from the Power Receiver. The Power Transmitter combines this information with information that it stores internally to construct a so-called Power Transfer Contract, which comprises various limits on the power transfer. In the *power transfer*

<sup>&</sup>lt;sup>2</sup>A definition of such a stand-by mode is outside the scope of this version 1.0.1 System Description Wireless Power Transfer, Volume I, Part 1. However, [Part 2] provides requirements on the maximum power use of a Power Transmitter when it is not actively providing power to a Power Receiver.

phase, the actual power transfer takes place. During this phase, the Power Transmitter and the Power Receiver cooperate to regulate the transferred power to the desired level. For this purpose, the Power Receiver communicates its power needs on a regular basis. In addition, the Power Transmitter continuously monitors the power transfer to ensure that the limits collected in the Power Transfer Contract are not violated. If a violation occurs anyway, the Power Transmitter aborts the power transfer.

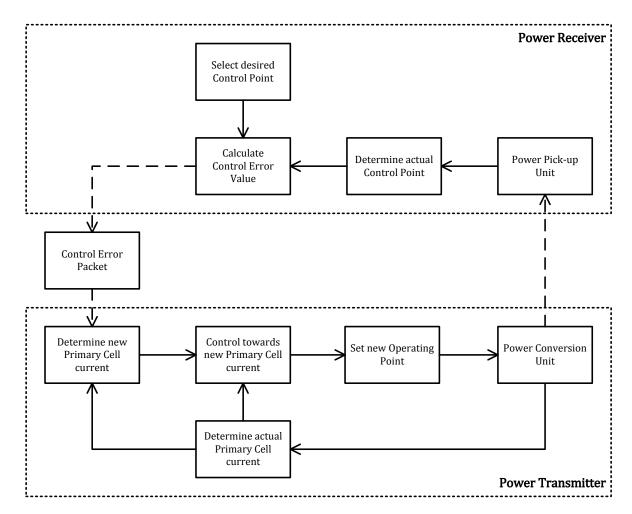

The various Power Transmitter designs employ different methods to adjust the transferred power to the requested level. Three commonly used methods include frequency control—the Primary Coil current, and thus the transferred power, is frequency dependent due to the resonant nature of the transformer—duty cycle control—the amplitude of the Primary Coil current scales with the duty cycle of the inverter that is used to drive it—and voltage control—the Primary Coil current scales with the driving voltage. Whereas the details of these control methods are defined in Section 3, Section 5 defines the overall error based control strategy. This means that the Power Receiver communicates the difference between a desired set point and the actual set point to the Power Transmitter, which adjusts the Primary Coil current so as to reduce the error towards zero. There are no constraints on how the Power Receiver derives its set point from parameters such as power, voltage, current, and temperature. This leaves the option to the Power Receiver to apply any desired control strategy.

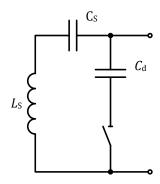

This version 1.0.1 of the System Description Wireless Power Transfer, Volume I, Part 1, defines communications from the Power Receiver to the Power Transmitter only. Section 6 defines the communications interface. On a physical level, communications from the Power Receiver to the Power Transmitter proceed using load modulation. This means that the Power Receiver switches the amount of power that it draws from the Power Transmitter between two discrete levels (note that these levels are not fixed, but depend on the amount of power that is being transferred). The actual load modulation method is left as a design choice to the Power Receiver. Resistive, capacitive, and inductive schemes are all possible. On a logical level, the communications protocol uses a sequence of short messages that contain the relevant data. These messages are contained in Packets, which are transmitted in a simple UART like format.

Annex A provides two example Power Receiver designs. The design shown in the first example directly provides the rectified voltage from the Secondary Coil to a single-cell lithium-ion battery for charging at constant current or voltage. The design shown in the second example uses a post-regulation stage to create a voltage source at the output of the Power Receiver.

This version 1.0.1 of the System Description Wireless Power Transfer, Volume I, Part 1, does not define how a Power Transmitter should detect an object that is placed on the Interface Surface. Annex B discusses several example methods that a Power Transmitter can use. Some of these methods enable Power Transmitter implementations that use very low stand-by power—if there are no Power Receivers present on the Interface Surface, or if there are Power Receivers present that are not engaged in power transfer.

Annex C discusses a few use cases that deal with locating Power Receivers on the Interface Surface of a type B Power Transmitter. In particular, these use cases describe how to find the optimum location for the Active Area—through which the Power Transmitter provides power to the Power Receiver—and how to distinguish between multiple closely spaced Power Receivers.

Finally, Annex D discusses how a Power Transmitter should detect the presence of foreign objects on the Interface Surface, which are sufficiently close to the Active Area to interfere with the power transfer. Typical examples of such foreign objects are parasitic metals such as coins, keys, paperclips, etc. If a parasitic metal is close to the Active Area it could heat up during power transfer due to eddy currents that result from the oscillating magnetic field. In order to prevent unsafe situations from developing, the Power Transmitter should abort the power transfer, before the temperature of the parasitic metal rises to unacceptable levels.

This page is intentionally left blank.

### 3 Basic Power Transmitter Designs

#### 3.1 Introduction

The Power Transmitter designs, which this version 1.0.1 of the System Description Wireless Power Transfer, Volume I, Part 1, defines, are grouped in two basic types.

Type A Power Transmitter designs have a single Primary Coil—and a single Primary Cell, which coincides with the Primary Coil. In addition, type A Power Transmitter designs include means to realize proper alignment of the Primary Coil and Secondary Coil. Depending on this means, a type A Power Transmitter enables either Guided Positioning or Free Positioning.

Type B Power Transmitter designs have an array of Primary Coils. All type B Power Transmitters enable Free Positioning. For that purpose, type B Power Transmitters can combine one or more Primary Coils from the array to realize a Primary Cell at different positions across the Interface Surface.

A Power Transmitter serves a single Power Receiver at a time only. However, a Base Station may contain several Power Transmitters in order to serve multiple Mobile Devices simultaneously. Note that multiple type B Power Transmitters may share (parts of) the multiplexer and array of Primary Coils (see Section 3.3.1.3).

#### 3.2 Power Transmitter designs that are based on a single Primary Coil

This Section 3.2 defines all type A Power Transmitter designs. In addition to the definitions in this Section 3.2, each Power Transmitter design shall implement the relevant parts of the protocols defined in Section 5, as well as the communications interface defined in Section 6.

#### 3.2.1 Power Transmitter design A1

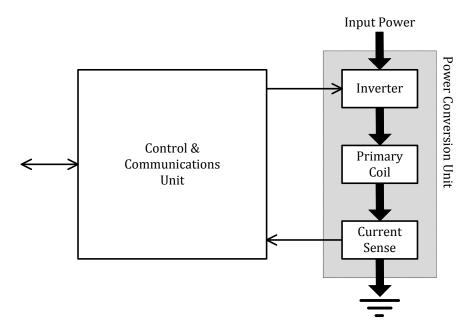

Power Transmitter design A1 enables Guided Positioning. Figure 3-1 illustrates the functional block diagram of this design, which consists of two major functional units, namely a Power Conversion Unit and a Communications and Control Unit.

Figure 3-1: Functional block diagram of Power Transmitter design A1

The Power Conversion Unit on the right-hand side of Figure 3-1 comprises the analog parts of the design. The inverter converts the DC input to an AC waveform that drives a resonant circuit, which consists of the Primary Coil plus a series capacitor. Finally, the current sense monitors the Primary Coil current.

The Communications and Control Unit on the left-hand side of Figure 3-1 comprises the digital logic part of the design. This unit receives and decodes messages from the Power Receiver, executes the relevant power control algorithms and protocols, and drives the frequency of the AC waveform to control the power transfer. The Communications and Control Unit also interfaces with other subsystems of the Base Station, e.g. for user interface purposes.

#### 3.2.1.1 Mechanical details

Power Transmitter design A1 includes a single Primary Coil as defined in Section 3.2.1.1.1, Shielding as defined in Section 3.2.1.1.2, an Interface Surface as defined in Section 3.2.1.1.3, and an alignment aid as defined in Section 3.2.1.1.4.

#### 3.2.1.1.1 Primary Coil

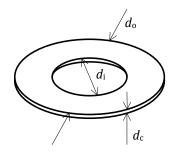

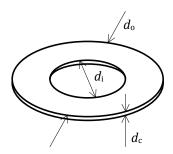

The Primary Coil is of the wire-wound type, and consists of no. 20 AWG (0.81 mm diameter) type 2 litz wire having 105 strands of no. 40 AWG (0.08 mm diameter), or equivalent. As shown in Figure 3-2, the Primary Coil has a circular shape and consists of multiple layers. All layers are stacked with the same polarity. Table 3-1 lists the dimensions of the Primary Coil.

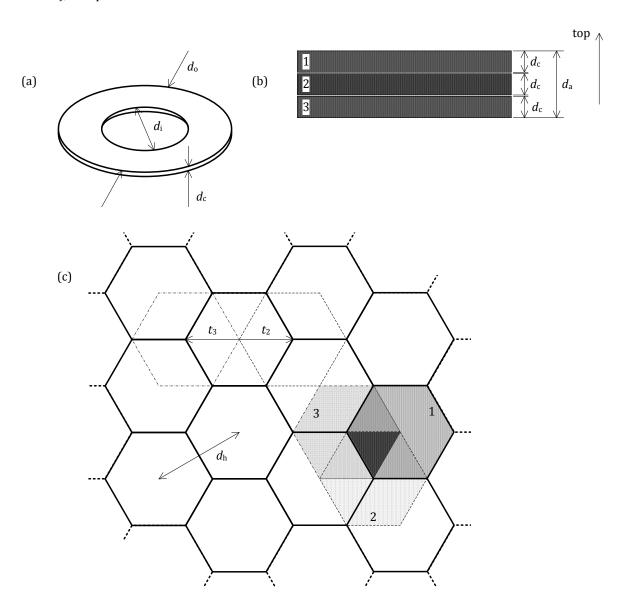

Figure 3-2: Primary Coil of Power Transmitter design A1

Table 3-1: Primary Coil parameters of Power Transmitter design A1

| Parameter                 | Symbol     | Value                   |

|---------------------------|------------|-------------------------|

| Outer diameter            | $d_{ m o}$ | 43 <sup>±0.5</sup> mm   |

| Inner diameter            | $d_{ m i}$ | 20.5 <sup>±0.5</sup> mm |

| Thickness                 | $d_{ m c}$ | 2.1 <sup>+0.5</sup> mm  |

| Number of turns per layer | N          | 10                      |

| Number of layers          | -          | 2                       |

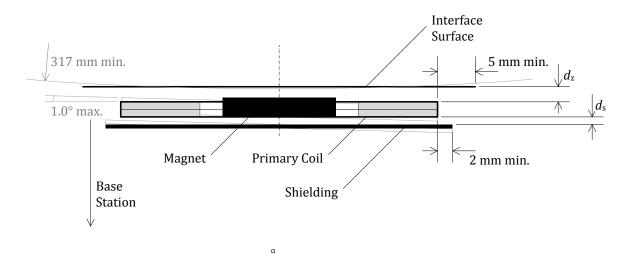

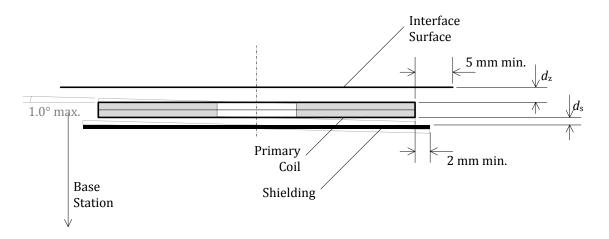

#### 3.2.1.1.2 Shielding

As shown in Figure 3-3, soft-magnetic material protects the Base Station from the magnetic field that is generated in the Primary Coil. The Shielding extends to at least 2 mm beyond the outer diameter of the Primary Coil, has a thickness of at least 0.5 mm, and is placed below the Primary Coil at a distance of at most  $d_{\rm s}=1.0$  mm. This version 1.0.1 of the System Description Wireless Power Transfer, Volume I, Part 1, limits the composition of the Shielding to a choice from the following list of materials:

- Material 44 Fair Rite Corporation.

- Material 28 Steward, Inc.

- CMG22G Ceramic Magnetics, Inc.

Figure 3-3: Primary Coil assembly of Power Transmitter design A1

#### 3.2.1.1.3 Interface Surface

As shown in Figure 3-3, the distance from the Primary Coil to the Interface Surface of the Base Station is  $d_z=2^{+0.5}_{-0.25}$  mm, across the top face of the Primary Coil. In addition, the Interface Surface of the Base Station extends at least 5 mm beyond the outer diameter of the Primary Coil. (Informative) This Primary-Coil-to-Interface-Surface distance implies that the tilt angle between the Primary Coil and a flat Interface Surface is at most 1.0°. Alternatively, in case of a non-flat Interface Surface, this Primary-Coil-to-Interface-Surface distance implies a radius of curvature of the Interface Surface of at least 317 mm, centered on the Primary Coil. See also Figure 3-3.

#### 3.2.1.1.4 Alignment aid

Power Transmitter design A1 employs a disc shaped bonded Neodymium magnet, which a Power Receiver design can exploit to provide an effective alignment means (see Section 4.2.1.2). As shown in Figure 3-3, the magnet is centered within the Primary Coil, and has its north pole oriented towards the Interface Surface. The (static) magnetic flux density due to the magnet, as measured across the Base Station's Interface Surface, has a maximum of  $100^{+50}_{-25}$  mT. The diameter of the magnet is at most 15.5 mm.

#### 3.2.1.1.5 Inter coil separation

If the Base Station contains multiple type A1 Power Transmitters, the Primary Coils of any pair of those Power Transmitters shall have a center-to-center distance of at least 50 mm.

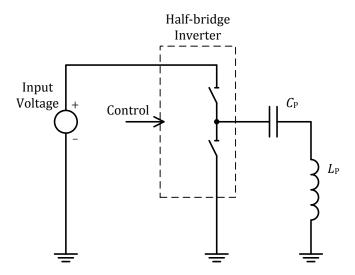

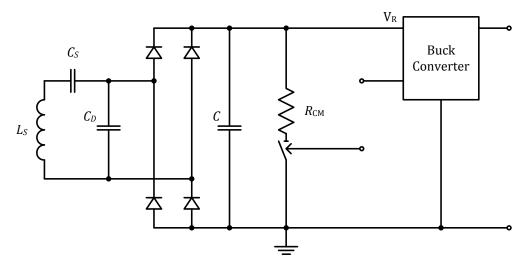

#### 3.2.1.2 Electrical details

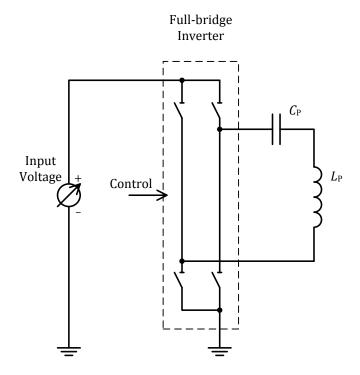

As shown in Figure 3-4, Power Transmitter design A1 uses a half-bridge inverter to drive the Primary Coil and a series capacitance. Within the Operating Frequency range specified below, the assembly of Primary Coil, Shielding, and magnet has a self inductance  $L_{\rm P}=24^{\pm10\%}$  µH. The value of the series capacitance is  $C_{\rm P}=100^{\pm5\%}$  nF. The input voltage to the half-bridge inverter is  $19^{\pm1}$  V. (Informative) Near resonance, the voltage developed across the series capacitance can reach levels exceeding 200 V pk-pk.

Power Transmitter design A1 uses the Operating Frequency and duty cycle of the Power Signal in order to control the amount of power that is transferred. For this purpose, the Operating Frequency range of the half-bridge inverter is  $f_{\rm op}=110\dots205$  kHz with a duty cycle of 50%; and its duty cycle range is 10...50% at an Operating Frequency of 205 kHz. A higher Operating Frequency or lower duty cycle result in the transfer of a lower amount of power. In order to achieve a sufficiently accurate adjustment of the amount of power that is transferred, a type A1 Power Transmitter shall control the Operating Frequency with a resolution of

•  $0.01 \times f_{op} - 0.7$  kHz, for  $f_{op}$  in the 110...175 kHz range;

•  $0.015 \times f_{op} - 1.58 \text{ kHz}$ , for  $f_{op}$  in the 175...205 kHz range;

or better. In addition, a type A1 Power Transmitter shall control the duty cycle of the Power Signal with a resolution of 0.1% or better.

When a type A1 Power Transmitter first applies a Power Signal (Digital Ping; see Section 5.2.1), it shall use an initial Operating Frequency of 175 kHz (and a duty cycle of 50%).

Control of the power transfer shall proceed using the PID algorithm, which is defined in Section 5.2.3.1. The controlled variable  $v^{(i)}$  introduced in the definition of that algorithm represents the Operating Frequency. In order to guarantee sufficiently accurate power control, a type A1 Power Transmitter shall determine the amplitude of the Primary Cell current—which is equal to the Primary Coil current—with a resolution of 7 mA or better. Finally, Table 3-2, Table 3-3, and Table 3-4 provide the values of several parameters, which are used in the PID algorithm.

Figure 3-4: Electrical diagram (outline) of Power Transmitter design A1

Table 3-2: PID parameters for Operating Frequency control

| Parameter           | Symbol           | Value  | Unit                              |

|---------------------|------------------|--------|-----------------------------------|

| Proportional gain   | $K_{\mathrm{p}}$ | 10     | mA-1                              |

| Integral gain       | K <sub>i</sub>   | 0.05   | mA <sup>-1</sup> ms <sup>-1</sup> |

| Derivative gain     | $K_{\mathrm{d}}$ | 0      | mA <sup>-1</sup> ms               |

| Integral term limit | $M_{ m I}$       | 3,000  | N.A.                              |

| PID output limit    | $M_{ m PID}$     | 20,000 | N.A.                              |

Table 3-3: Operating Frequency dependent scaling factor

| Frequency Range [kHz] | Scaling Factor S <sub>v</sub> [Hz] |

|-----------------------|------------------------------------|

| 110140                | 1.5                                |

| 140160                | 2                                  |

| 160180                | 3                                  |

| 180205                | 5                                  |

Table 3-4: PID parameters for duty cycle control

| Parameter           | Symbol           | Value  | Unit                              |

|---------------------|------------------|--------|-----------------------------------|

| Proportional gain   | $K_{\mathrm{p}}$ | 10     | mA-1                              |

| Integral gain       | $K_{\rm i}$      | 0.05   | mA <sup>-1</sup> ms <sup>-1</sup> |

| Derivative gain     | $K_{\mathrm{d}}$ | 0      | mA <sup>-1</sup> ms               |

| Integral term limit | $M_{\mathrm{I}}$ | 3,000  | N.A.                              |

| PID output limit    | $M_{ m PID}$     | 20,000 | N.A.                              |

| Scaling factor      | $S_{ m v}$       | -0.01  | %                                 |

#### 3.2.2 Power Transmitter design A2

Power Transmitter design A2 enables Free Positioning. Figure 3-5 illustrates the functional block diagram of this design, which consists of three major functional units, namely a Power Conversion Unit, a Detection Unit, and a Communications and Control Unit.

Figure 3-5: Functional block diagram of Power Transmitter design A2

The Power Conversion Unit on the right-hand side of Figure 3-5 and the Detection Unit of the bottom of Figure 3-5 comprise the analog parts of the design. The Power Conversion Unit is similar to the Power Conversion Unit of Power Transmitter design A1. The inverter converts the DC input to an AC waveform that drives a resonant circuit, which consists of the Primary Coil plus a series capacitor. The Primary Coil is mounted on a positioning stage to enable accurate alignment of the Primary Coil to the Active Area of the Mobile Device. Finally, the voltage sense monitors the Primary Coil voltage.

The Communications and Control Unit on the left-hand side of Figure 3-5 comprises the digital logic part of the design. This unit is similar to the Communications and Control Unit of Power Transmitter design A1. The Communications and Control Unit receives and decodes messages from the Power Receiver, executes the relevant power control algorithms and protocols, and drives the input voltage of the AC waveform to control the power transfer. In addition, the Communications and Control Unit drives the positioning stage and operates the Detection Unit. The Communications and Control Unit also interfaces with other subsystems of the Base Station, e.g. for user interface purposes.

The Detection Unit determines the approximate location of objects and/or Power Receivers on the Interface Surface. This version 1.0.1 of the System Description Wireless Power Transfer, Volume I, Part 1, does not specify a particular detection method. However, it is recommended that the Detection Unit exploits the resonance in the Power Receiver at the detection frequency  $f_{\rm d}$  (see Section 4.2.2.1). The

reason is that this approach minimizes movements of the Primary Coil, because the Power Transmitter does not need to attempt to identify objects that do not respond at this resonant frequency. Annex C.3 provides an example resonant detection method.

#### 3.2.2.1 Mechanical details

Power Transmitter design A2 includes a single Primary Coil as defined in Section 3.2.2.1.1, Shielding as defined in Section 3.2.2.1.2, an Interface Surface as defined in Section 3.2.2.1.3, and a positioning stage as defined in Section 3.2.2.1.4.

#### 3.2.2.1.1 **Primary Coil**

The Primary Coil is of the wire-wound type, and consists of litz wire having 30 strands of 0.1 mm diameter, or equivalent. As shown in Figure 3-6, the Primary Coil has a circular shape and consists of multiple layers. All layers are stacked with the same polarity. Table 3-5 lists the dimensions of the Primary Coil.

Figure 3-6: Primary Coil of Power Transmitter design A2

Table 3-5: Primary Coil parameters of Power Transmitter design A2

| Parameter                 | Symbol     | Value                  |

|---------------------------|------------|------------------------|

| Outer diameter            | $d_{ m o}$ | $40^{\pm 1}~\text{mm}$ |

| Inner diameter            | $d_{ m i}$ | $19^{\pm 1}$ mm        |

| Thickness                 | $d_{ m c}$ | 2 <sup>+0.2</sup> mm   |

| Number of turns per layer | N          | 10                     |

| Number of layers          | -          | 2                      |

#### 3.2.2.1.2 Shielding

As shown in Figure 3-7, soft-magnetic material protects the Base Station from the magnetic field that is generated in the Primary Coil. The Shielding extends to at least 2 mm beyond the outer diameter of the Primary Coil, has a thickness of at least 0.20 mm and is placed below the Primary Coil at a distance of at most  $d_{\rm s}=0.1$  mm. This version 1.0.1 of the System Description Wireless Power Transfer, Volume I, Part 1, limits the composition of the Shielding to a choice from the following list of materials:

- DPR-MF3 Daido Steel

- HS13-H Daido Steel

Figure 3-7: Primary Coil assembly of Power Transmitter design A2

#### 3.2.2.1.3 Interface Surface

As shown in Figure 3-7, the distance from the Primary Coil to the Interface Surface of the Base Station is  $d_z = 2.5^{+0.5}_{-0}$  mm, across the top face of the Primary Coil. In addition, the Interface Surface of the Base Station extends at least 5 mm beyond the outer diameter of the Primary Coil.

#### 3.2.2.1.4 Positioning stage

The positioning stage shall have a resolution of 0.1 mm or better in each of the two orthogonal directions parallel to the Interface Surface.

#### 3.2.2.2 Electrical details

As shown in Figure 3-8, Power Transmitter design A2 uses a full-bridge inverter to drive the Primary Coil and a series capacitance. At the fixed Operating Frequency of 140 kHz, the assembly of Primary Coil and Shielding has a self inductance  $L_P=24^{\pm1}\,\mu\text{H}$ . The value of the series capacitance is  $C_P=200^{\pm5\%}\,\text{nF}$ . (Informative) Near resonance, the voltage developed across the series capacitance can reach levels up to  $50\,V\,pk$ -pk.

Power Transmitter design A2 uses the input voltage to the full-bridge inverter to control the amount of power that is transferred. For this purpose, the input voltage range is 3...12 V, where a lower input voltage results in the transfer of a lower amount of power. In order to achieve a sufficiently accurate adjustment of the power that is transferred, a type A2 Power Transmitter shall be able to control the input voltage with a resolution of 50 mV or better.

When a type A2 Power Transmitter first applies a Power Signal (Digital Ping; see Section 5.2.1), it shall use an initial input voltage of 8 V.

Figure 3-8: Electrical diagram (outline) of Power Transmitter design A2

Control of the power transfer shall proceed using the PID algorithm, which is defined in Section 5.2.3.1. The controlled variable  $v^{(i)}$  introduced in the definition of that algorithm represents the input voltage to the full-bridge inverter. In order to guarantee sufficiently accurate power control, a type A2 Power Transmitter shall determine the amplitude of the Primary Cell voltage—which is equal to the Primary Coil voltage—with a resolution of 5 mV or better. Finally, Table 3-6 provides the values of several parameters, which are used in the PID algorithm.

Table 3-6: PID parameters for voltage control

| Parameter           | Symbol           | Value | Unit                              |

|---------------------|------------------|-------|-----------------------------------|

| Proportional gain   | $K_{\mathrm{p}}$ | 1     | mA <sup>-1</sup>                  |

| Integral gain       | $K_{\rm i}$      | 0     | mA <sup>-1</sup> ms <sup>-1</sup> |

| Derivative gain     | $K_{\mathrm{d}}$ | 0     | mA <sup>-1</sup> ms               |

| Integral term limit | $M_{\mathrm{I}}$ | N.A.  | N.A.                              |

| PID output limit    | $M_{ m PID}$     | 1,500 | N.A.                              |

| Scaling factor      | $S_{ m v}$       | -0.5  | mV                                |

#### 3.3 Power Transmitter designs that are based on an array of Primary Coils

This Section 3.3 defines all type B Power Transmitter designs. In addition to the definitions in this Section 3.3, each Power Transmitter design shall implement the relevant parts of the protocols defined in Section 5, as well as the communications interface defined in Section 6.

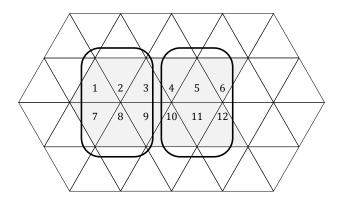

#### 3.3.1 Power Transmitter design B1

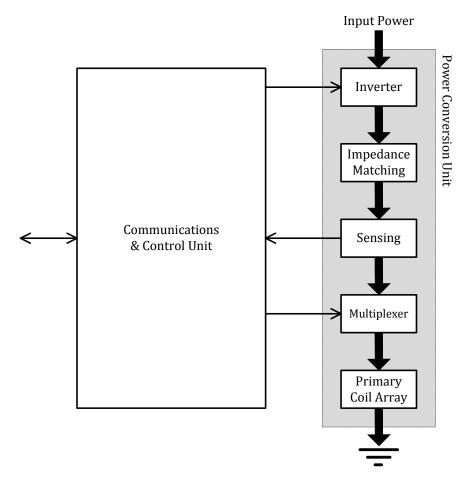

Power Transmitter design B1 enables Free Positioning. Figure 3-9 illustrates the functional block diagram of this design, which consists of two major functional units, namely a Power Conversion Unit and a Communications and Control Unit.

Figure 3-9: Functional block diagram of Power Transmitter design B1

The Power Conversion Unit on the right-hand side of Figure 3-9 comprises the analog parts of the design. The design uses an array of partly overlapping Primary Coils to provide for Free Positioning. Depending on the position of the Power Receiver, the multiplexer connects and/or disconnects the appropriate Primary Coils. The impedance matching network forms a resonant circuit with the parts of the Primary Coil array that are connected. The sensing circuits monitor (amongst others) the Primary Cell current and voltage, and the inverter converts the DC input to an AC waveform that drives the Primary Coil array.

The Communications and Control Unit on the left-hand side of Figure 3-9 comprises the digital logic part of the design. This unit receives and decodes messages from the Power Receiver, configures the multiplexer to connect the appropriate parts of the Primary Coil array, executes the relevant power control algorithms and protocols, and drives the frequency and input voltage to the inverter to control the amount of power provided to the Power Receiver. The Communications and Control Unit also interfaces with the other subsystems of the Base Station, e.g. for user interface purposes.

#### 3.3.1.1 Mechanical details

Power Transmitter design B1 includes a Primary Coil array as defined in Section 3.3.1.1.1, Shielding as defined in Section 3.3.1.1.2, and an Interface Surface as defined in Section 3.3.1.1.3.

#### 3.3.1.1.1 Primary Coil array

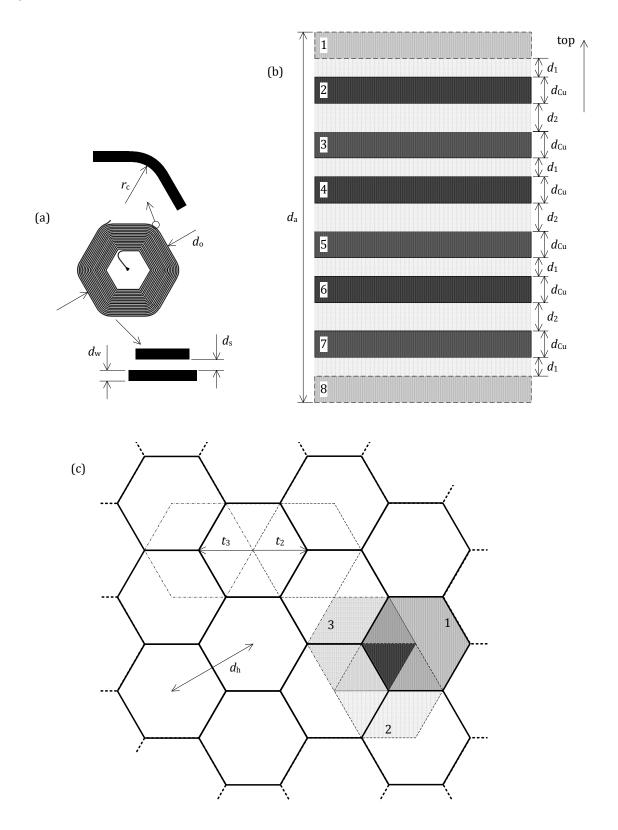

The Primary Coil array consists of 3 layers. Figure 3-10(a) shows a top view of a single Primary Coil, which is of the wire-wound type, and consists of litz wire having 24 strands of no. 40 AWG (0.08 mm diameter), or equivalent.

Figure 3-10: Primary Coil array of Power Transmitter design B1

As shown in Figure 3-10(a), the Primary Coil has a circular shape and consists of a single layer. Figure 3-10(b) shows a side view of the layer structure of the Primary Coil array. Figure 3-10(c) provides a top view of the Primary Coil array, showing that the individual Primary Coils are packed in a hexagonal grid. The solid hexagons show the closely packed structure of the grid of Primary Coils on layer 1 of the Primary Coil array. The dashed hexagon illustrates that the grid of Primary Coils on layer 2 is offset over a distance  $t_2$  to the right, such that the centers of the Primary Coils in layer 2 coincide with the corners of

Primary Coils in layer 1. Likewise, the dash-dotted hexagon illustrates that the grid of Primary Coils on layer 3 is offset over a distance  $t_3$  to the left, such that the centers of the Primary Coils in layer 3 coincide with the corners of Primary Coils in layer 1. As a result, the centers, respectively corners, of the Primary Coils on layer 2 and the corners, respectively centers, of the Primary Coils on layer 3 coincide as well. All Primary Coils are stacked with the same polarity. See Section 3.3.1.2 for the meaning of the shaded hexagons.

Table 3-7 lists the relevant parameters of the Primary Coil array.

| Parameter                          | Symbol           | Value                                   |

|------------------------------------|------------------|-----------------------------------------|

| Outer diameter                     | $d_{ m o}$       | 28.5 <sub>-0.7</sub> mm                 |

| Inner diameter                     | $d_{ m i}$       | 10.5 <sup>±0.3</sup> mm                 |

| Layer thickness*                   | $d_{ m c}$       | 0.6 <sup>+0.05</sup> <sub>-0.1</sub> mm |

| Number of turns                    | N                | 16                                      |

| Array thickness                    | $d_{\mathrm{a}}$ | 1.9 <sup>+0.3</sup> <sub>-0.2</sub> mm  |

| Center-to-center distance          | $d_{ m h}$       | 28.6 <sup>+1</sup> mm                   |

| Offset 2 <sup>nd</sup> layer array | t <sub>2</sub>   | 16.5 <sup>+0.6</sup> mm                 |

| Offset 3 <sup>rd</sup> layer array | $t_3$            | 16.5 <sup>+0.6</sup> mm                 |

\*Value includes thickness of connection wires

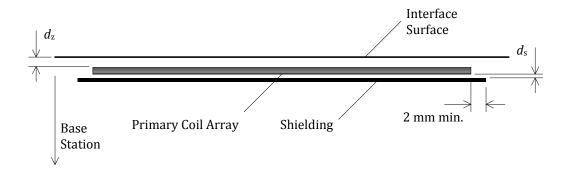

#### 3.3.1.1.2 Shielding

As shown in Figure 3-11, Transmitter design B1 employs Shielding to protect the Base Station from the magnetic field that is generated in the Primary Coil array. The Shielding extends to at least 2 mm beyond the outer edges of the Primary Coil array, and is placed at a distance of at most  $d_{\rm s}=0.5$  mm below the Primary Coil array.

The Shielding consists of soft magnetic material that has a thickness of at least 0.5 mm. This version 1.0.1 of the System Description Wireless Power Transfer, Volume I, Part 1, limits the composition of the Shielding to a choice from the following list of materials:

- Material 78 Fair Rite Corporation.

- 3C94 Ferroxcube.

- N87 Epcos AG.

- PC44 TDK Corp.

Figure 3-11: Primary Coil array assembly of Power Transmitter design B1

#### 3.3.1.1.3 Interface Surface

As shown in Figure 3-11, the distance from the Primary Coil array to the Interface Surface of the Base Station is  $d_z = 2^{+0.5}_{-0.25}$  mm, across the top face of the Primary Coil array. In addition, the Interface Surface extends at least 5 mm beyond the outer edges of the Primary Coil array.

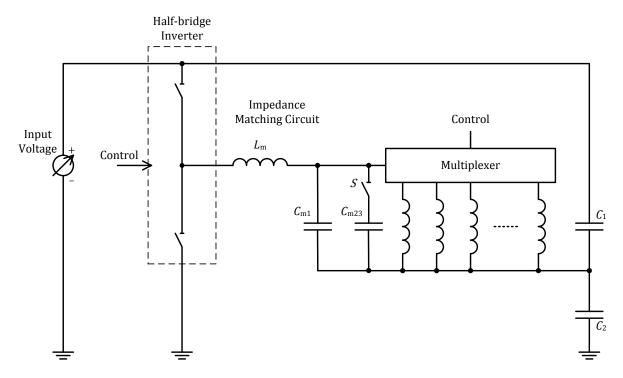

#### 3.3.1.2 Electrical details

As shown in Figure 3-12, Power Transmitter design B1 uses a half-bridge inverter to drive the Primary Coil array. In addition, Power Transmitter design B1 uses a multiplexer to select the position of the Active Area. The multiplexer shall configure the Primary Coil array in such a way that one, two, or three Primary Coils are connected—in parallel—to the driving circuit. The connected Primary Coils together constitute a Primary Cell. As an additional constraint, the multiplexer shall select the Primary Coils such that each selected Primary Coil has an overlap with every other selected Primary Coil; see Figure 3-10(c) for an example.

Figure 3-12: Electrical diagram (outline) of Power Transmitter design B1

Within the Operating Frequency range  $f_{\rm op}=105\dots 113$  kHz, the assembly of Primary Coil array and Shielding has an inductance of  $8.1^{\pm 1}$   $\mu{\rm H}$  for each individual Primary Coil in layer 1 (closest to the Interface Surface),  $8.7^{\pm 1}$   $\mu{\rm H}$  for each individual Primary Coil in layer 2, and  $9.6^{\pm 1}$   $\mu{\rm H}$  for each individual Primary Coil in layer 3. The capacitances and inductance in the impedance matching circuit are, respectively,  $C_{\rm m1}=300^{\pm 5\%}$  nF,  $C_{\rm m23}=200^{\pm 5\%}$  nF,and  $L_{\rm m}=3.8^{\pm 5\%}$   $\mu{\rm H}$ . The capacitances  $C_1$  and  $C_2$  in the half-bridge inverter both are  $68~\mu{\rm F}$ . The switch S is open if the Primary Cell consists of a single Primary Coil; otherwise, the swich S is closed. (Informative) The voltage across the capacitance  $C_{\rm m}$  can reach levels exceeding 36~V pk-pk.

Power Transmitter design B1 uses the input voltage to the half-bridge inverter to control the amount of power that is transferred. For this purpose, the input voltage range is 0...20 V, where a lower input voltage results in the transfer of a lower amount of power. In order to achieve a sufficiently accurate adjustment of the power that is transferred, a type B1 Power Transmitter shall be able to control the input voltage with a resolution of 35 mV or better.

When a type B1 Power Transmitter first applies a Power Signal (Digital Ping; see Section 5.2.1), it shall use an initial input voltage of 12 V.

Control of the power transfer shall proceed using the PID algorithm, which is defined in Section 5.2.3.1. The controlled variable  $v^{(i)}$  introduced in the definition of that algorithm represents the input voltage to the half-bridge inverter. In order to guarantee sufficiently accurate power control, a type B1 Transmitter shall determine the amplitude of the current into the Primary Cell with a resolution of 5 mA or better. In addition to the PID algorithm, a type B1 Power Transmitter shall limit the current into the Primary Cell to at most 4 A RMS in the case that the Primary Cell consists of two or three Primary Coils, or at most 2 A RMS in the case that the Primary Cell consists of one Primary Coil. For that purpose, the Power Transmitter may limit the input voltage to the half-bridge inverter to value that is lower than 20 V. Finally, Table 3-8 provides the values of several parameters, which are used in the PID algorithm.

**Symbol Parameter** Value Unit Proportional gain  $K_{\rm p}$ 1 mA-1  $mA^{-1}ms^{-1}$ 0 Integral gain  $K_{i}$ 0 Derivative gain  $K_{\rm d}$ mA-1ms  $M_{\rm I}$ N.A. Integral term limit N.A. PID output limit  $M_{\rm PID}$ 2.000 N.A.

$S_{\rm v}$

-1

$\, mV \,$

Table 3-8: PID parameters for voltage control

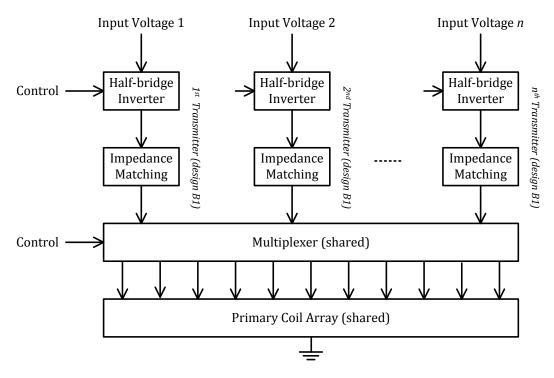

#### 3.3.1.3 Scalability

Scaling factor

Sections 3.3.1.1 and 3.3.1.2 define the mechanical and electrical details of Power Transmitter design B1. As defined in Section 3.1, a type B1 Power Transmitter serves a single Power Receiver only. In order to serve multiple Power Receivers simultaneously, a Base Station may contain multiple type B1 Power Transmitters. As shown in Figure 3-13, these Power Transmitters may share the Primary Coil array and multiplexer. However, each individual Power Transmitter shall have a separately controllable inverter, impedance matching circuit, and means to determine the Primary Cell current, as defined in Section 3.3.1.2. In addition, the multiplexer shall ensure that it does not connect multiple inverters to any individual Primary Coil.

Figure 3-13: Multiple type B1 Power Transmitters sharing a multiplexer and Primary Coil array

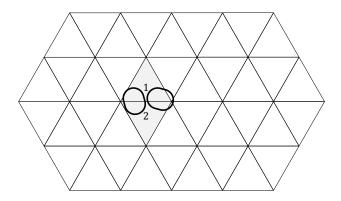

#### 3.3.2 Power Transmitter design B2

Power Transmitter design B2 enables Free Positioning. The main difference between Power Transmitter design B2 and Power Transmitter design B1 is the Primary Coil array. Power Transmitter design B2 is based on a Printed Circuit Board (PCB) type Primary Coil array. The functional block diagram of a type B2 Power Transmitter is identical to the functional block diagram of a type B1 Power Transmitter; see Figure 3-9 and the descriptive text in Section 3.3.1.

#### 3.3.2.1 Mechanical details

Power Transmitter design B2 includes a Primary Coil array as defined in Section 3.3.2.1.1, Shielding as defined in Section 3.3.2.1.2, and an Interface Surface as defined in Section 3.3.2.1.3.

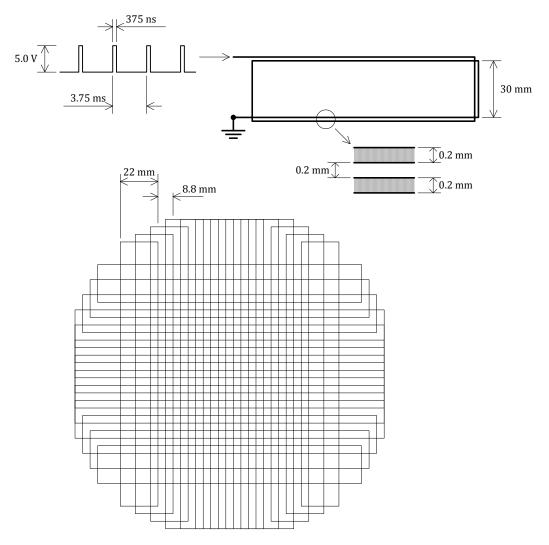

#### 3.3.2.1.1 Primary Coil array

The Primary Coil array consists of a 8 layer PCB. The inner six layers of the PCB each contain a grid of Primary Coils, and the bottom layer contains the leads to each of the individual Primary Coils. The top layer can be used for any purpose, but shall not influence the inductance values of the Primary Coils. Figure 3-14(a) shows a top view of a single Primary Coil, which consists of a trace that runs through 18 hexagonal turns. As shown in the top inset of Figure 3-14(a), the corners of this hexagonal shape are rounded. The bottom inset of Figure 3-14(a) shows the width of the trace as well as the distance between two adjacent turns. Figure 3-14(b) shows a side view of the layer structure of the PCB. Copper layers 2, 3, 4, 5, 6, and 7 each contain a grid of Primary Coils. Copper layer 8 contains the leads to each of the Primary Coils. Figure 3-14(c) provides a top view of the Primary Coil array, showing that the individual Primary Coils are packed in a hexagonal grid. The solid hexagons show the closely packed structure of the grids of Primary Coils on layer 2 and layer 7 of the Primary Coil array. Each solid hexagon represents a set of two identical Primary Coils—in this case one Primary Coil on layer 2 and one Primary Coil on layer 7. respectively—which are connected in parallel. The dashed hexagon illustrates that the grids of Primary Coils on layer 3 and layer 6 are offset over a distance  $t_2$  to the right, such that the centers of the Primary Coils in layer 3 and layer 6 coincide with the corners of Primary Coils in layer 2 and layer 7. Likewise, the dash-dotted hexagon illustrates that the grids of Primary Coils on layer 4 and layer 5 are offset over a distance  $t_3$  to the left, such that the centers of the Primary Coils in layer 4 and layer 5 coincide with the corners of Primary Coils in layer 2 and layer 7. As a result, the centers, respectively corners, of the Primary Coils on layer 3 and layer 6 and the corners, respectively centers, of the Primary Coils on layer 4 and layer 5 coincide as well. See Section 3.3.2.2 for the meaning of the shaded hexagons.

Table 3-9: Primary Coil array parameters of Power Transmitter design B2

| Parameter                          | Symbol            | Value                                   |  |

|------------------------------------|-------------------|-----------------------------------------|--|

| Outer diameter                     | $d_{ m o}$        | $31^{\pm 0.4} \text{ mm}$               |  |

| Track width                        | $d_{ m w}$        | $0.42^{\pm0.03} \text{ mm}$             |  |

| Track width plus spacing           | $d_w + d_s$       | $0.6^{\pm0.03} \text{ mm}$              |  |

| Corner rounding*                   | $r_{ m c}$        | 5 <sup>±3</sup> mm                      |  |

| Number of turns                    | N                 | 18                                      |  |

| Track thickness                    | $d_{\mathrm{Cu}}$ | $0.07^{\pm0.014}  \mathrm{mm}$          |  |

| Dielectric thickness 1             | $d_{ m d1}$       | 0.089 <sup>+0.15</sup> <sub>-0</sub> mm |  |

| Dielectric thickness 2             | $d_{ m d2}$       | $0.1^{\pm 0.013} \text{ mm}$            |  |

| Array thickness                    | $d_{\mathrm{a}}$  | $1.14^{\pm0.05}$ mm                     |  |

| Center-to-center distance          | $d_{ m h}$        | 31.855 <sup>±0.2</sup> mm               |  |

| Offset 2 <sup>nd</sup> layer array | $t_2$             | 18.4±0.1 mm                             |  |

| Offset 3 <sup>rd</sup> layer array | $t_3$             | 18.4 <sup>±0.1</sup> mm                 |  |

\*Value applies to the outermost winding

Table 3-9 lists the relevant parameters of the Primary Coil array. The finished PCB thickness is  $1.3^{\pm 10\%}\,\text{mm}.$

Figure 3-14: Primary Coil array of Power Transmitter design B2

#### **3.3.2.1.2** Shielding

Power Transmitter design B2 employs Shielding that is identical to the Shielding of Power Transmitter design B1. See Section 3.3.1.1.2.

#### 3.3.2.1.3 Interface Surface

The distance from the Primary Coil array to the Interface Surface of the Base Station is  $d_z = 2^{+0.1}_{-0.5}$  mm, across the top face of the Primary Coil array. See also Figure 3-11 in Section 3.3.1.1.3. In addition, the Interface Surface extends at least 5 mm beyond the outer edges of the Primary Coil array.

#### 3.3.2.2 Electrical details

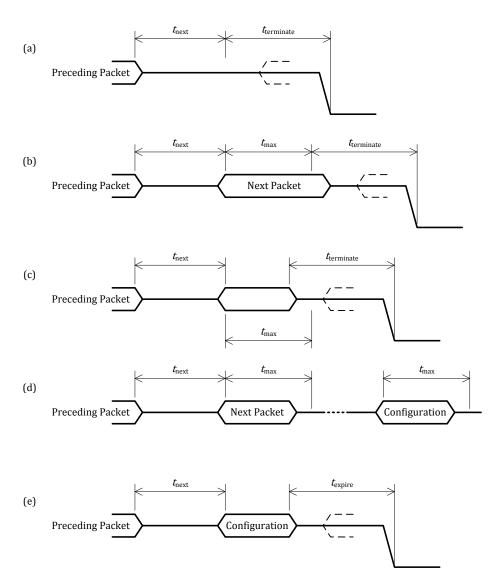

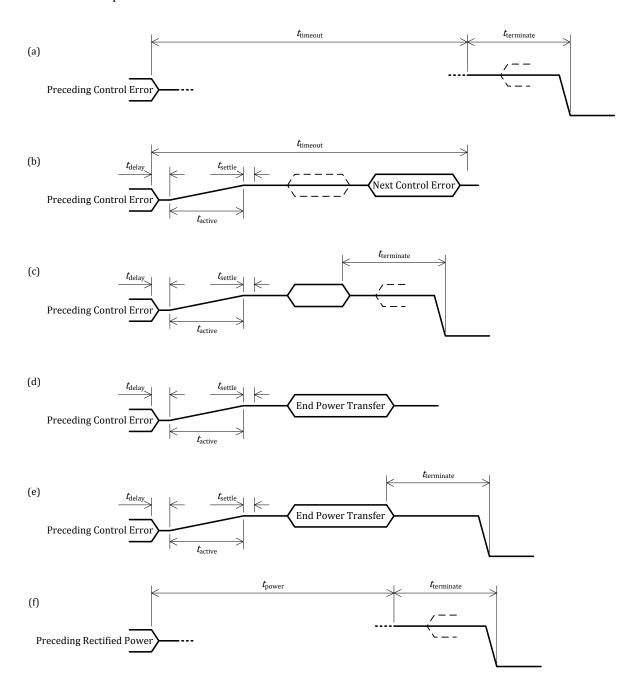

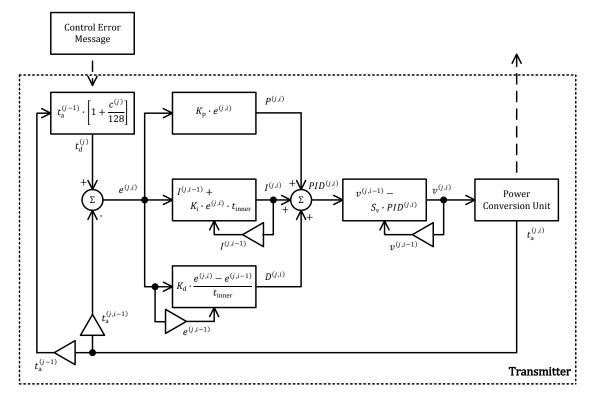

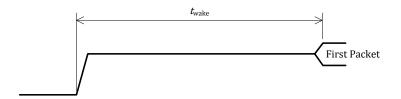

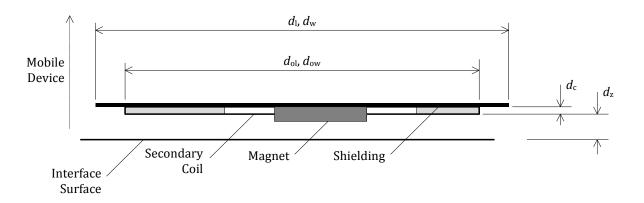

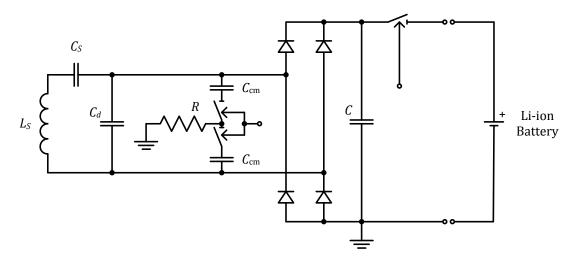

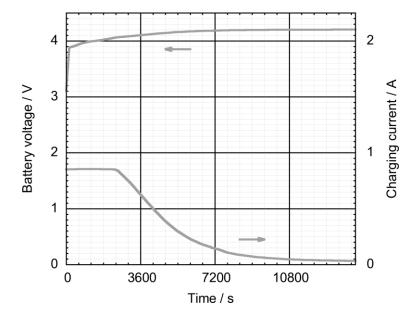

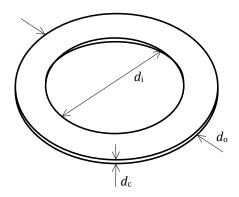

The outline of the electrical diagram of Power Transmitter design B2 follows the outline of the electrical diagram of Power Transmitter design B1. See also Figure 3-12 in Section 3.3.1.2.